Apresentação

Mestrado e Doutorado Acadêmico · Stricto Sensu

A região do Grande ABC do Estado de São Paulo consiste em uma das regiões mais industrializadas do País, com presença forte da indústria automobilística e de suas fornecedoras, indústrias do ramo eletro-eletrônico, entre outras atividades. Há uma demanda crescente das indústrias da região e em todo o Brasil por recursos humanos de alto nível, capazes de promover e desenvolver pesquisa aplicada em Engenharia, especialmente em Microeletrônica e Tecnologia da Informação.

O Programa de Pós-Graduação Stricto Sensu em Engenharia Elétrica da FEI tem como objetivo formar docentes e pesquisadores, nos níveis de Mestrado e Doutorado, com conhecimento científico nas seguintes áreas de concentração: Nanoeletrônica e Circuitos Integrados, Inteligência Artificial Aplicada à Automação e Robótica e Processamento de Sinais e Imagens

Mais especificamente, o programa visa:

- Promover e desenvolver a pesquisa aplicada em Microeletrônica, Automação e Processamento de Sinais, incentivando produções intelectuais e tecnológicas e a disseminação dessas produções em periódicos e congressos nacionais/internacionais de relevância científica para a área de Engenharia Elétrica;

- Constituir grupos de pesquisas e desenvolvimento de alto nível científico, capazes de propor soluções inovadoras para problemas encontrados na indústria e na academia relacionados, por exemplo, com projeto de circuitos dedicados (digitais e analógicos), caracterização elétrica de dispositivos eletrônicos, automação de processos industriais, robotização, sistemas inteligentes, reconhecimento de padrões e processamento digital de sinais;

- Capacitar recursos humanos para a docência em Microeletrônica, Inteligência Artificial, Robótica e Processamento de Sinais, melhorando a qualidade do ensino superior nessas áreas de interesse, principalmente na região do Grande ABC.

Os cursos de Mestrado e Doutorado são projetados tanto para alunos em tempo integral (com possibilidade de bolsas CAPES, CNPq, FAPESP e Institucional), como para profissionais que atuam no mercado de trabalho, com disciplinas em período noturno.

Espera-se do profissional a ser formado características de pesquisa e desenvolvimento não somente para disseminação e atualização de conhecimento científico nas universidades como docente, mas também para evolução desse conhecimento, institutos de pesquisa e empresas, como pesquisador com capacidade de conceber, participar e interagir com processos de inovação tecnológica nas áreas de concentração do programa.

Coordenador: Profº. Drº. Carlos Eduardo Thomaz

Descrição do Programa

Nível Mestrado

(aprovado pela CAPES - ofício 327/2004/CTC/CAPES)

Nível Doutorado

(aprovado pela CAPES - ofício nº010-06/2012/CTC/CAAIII/CGAA/DAV/CAPES)

Estrutura do Curso

Mestrado

O Curso de Mestrado demandará um total de 40 unidades de crédito em disciplinas e atividades programadas obrigatórias, compreendendo:

- 6 disciplinas (24 créditos), preferencialmente cursadas no primeiro, segundo e terceiro quadrimestres acadêmicos.

- 4 unidades de crédito serão atribuídas à apresentação e aprovação do Exame de Qualificação pela Banca Examinadora.

- 12 unidades de crédito são atribuídas à Defesa Pública e aprovação pela Banca Examinadora da Dissertação de Mestrado, totalizando os 40 créditos mínimos requeridos.

Doutorado

O Curso de Doutorado demandará um total de 44 unidades de créditos em disciplinas e atividades programadas, compreendendo:

- 4 disciplinas (16 créditos), preferencialmente cursadas no primeiro, segundo e terceiro quadrimestres acadêmicos;

- 4 unidades de crédito atribuídas à apresentação e aprovação do Exame de Qualificação pela Banca Examinadora;

- 24 unidades de crédito atribuídas à Defesa Pública e aprovação pela Banca Examinadora da Tese de Doutorado, totalizando os 44 créditos mínimos requeridos.

Definição do Orientador

Mestrado

O aluno ingressante no Programa de Pós-Graduação poderá imediatamente definir seu professor orientador, formalizando o pedido de orientação junto à Secretaria de Pós-Graduação, acompanhado da anuência do orientador e a devida aprovação do Coordenador de Programa. Caso o orientador não seja definido inicialmente, durante o período em que cursar as disciplinas, o aluno será orientado pelo Coordenador do Programa, ou por professor por ele designado.

Doutorado

A definição do orientador é um dos requisitos para ingressar no programa, a oficialização do orientador deverá acontecer no ato da matrícula.

Parcerias

Programa de Atualização de E-CAD para Instituições de Ensino Superior Coordenada pela Sociedade Brasileira de Microeletronica (SBMicro) - Cadence

Centro Universitário FEI / CADENCE University Program Member

Coordenador/Coordenator/Responsable for the site: Prof. Dr. Salvador Pinillos Gimenez and Prof. Dr. Renato C. Giacomini

Integrated Electronics Devices

Electrical Engineering Department

Centro Universitario FEI

Av. Humberto de Alencar Castelo Branco, 3972 - Assunção

Sao Bernardo do Campo - Sao Paulo - Brazil - CEP 09850-901

Tel: +55 (0)11 4353 2910 (ext. 2184)

Fax: +55 (0)11 4109 5994

Email: sgimenez@fei.edu.br

Projeto: Projetos de Circuitos Integrados Digitais com Geração Automática de Leiaute Utilizando-se as Ferramentas CADENCE (Custom IC and Digital IC) – Prof. Dr. Salvador Pinillos Gimenez

Project: Digital Integrated Circuits Design with Automatic Layout Generation Using the CADENCE EDA Tools (Custom IC and Digital IC) - Prof. Salvador Pinillos Gimenez, PhD

O objetivo deste projeto é implementar o leiaute de circuitos integrados digitais de forma automática a partir de um arquivo VHDL/VERILOG, utilizando-se as ferramentas CADENCE. Além disso, uma meta bastante importante desse projeto é a formação de recursos humanos de alunos de iniciação científica, mestrado e doutorado na área de projeto/simulação/leiaute/fabricação de circuitos integrados utilizando-se as ferramentas da CADENCE.

The objective of this project is to implement automatically layouts of digital integrated circuits with the use of CADENCE EDA tools. Besides that, other very important goal of this project is the generation of human resources regarding scientific students, master students and PhD students in the design/simulation/layout/manufacturing of integrated circuits using CADENCE EDA tools.

Dois alunos de Mestrado (FILIPE ANTOINE KHATCHADOURIAN e VICTOR SIQUEIRA MARTINS BRAGA) trabalharam com as ferramentas CADENCE para a geração automática de leiaute de um microcontrolador 8051, conforme ilustrado na Figura 1.

Projeto finalizado em 2015.

Two Masters Students (FILIPE ANTOINE KHATCHADOURIAN e VICTOR SIQUEIRA MARTINS BRAGA) work with the CADENCE tools to generate automatically the 8051 microcontroller, as illustrated in Figure 1.

Figura 1. Leiaute do 8051 gerado com as ferramentas da CADENCE.

Figure 1. The 8051 microcontroller layout implemented with the CADENCE tools.

Others students will continue being trained with the CADENCE tools in order to design integrated circuits at FEI University Center (Centro Universitário FEI).

FEI University Center acknowledges CADENCE by the opportunity to participate of the University Program.

Project completed in 2015.

Projeto: Arquitetura de CPU Inovadora Focada em Sistemas de Tempo Real – Prof. Dr. Salvador Pinillos Gimenez.

Project: Innovative CPU Architecture Focused on Real-Time Systems – Prof. Salvador Pinillos Gimenez, PhD.

Este trabalho propõe uma nova técnica e arquitetura de hardware para controle de multitarefas em sistemas de tempo real (RTS) desenvolvidos para execução em microprocessadores ou microcontroladores de núcleo único. Tem como um dos objetivos implementar o leiaute de um processador digital de forma automática a partir de um arquivo VHDL/VERILOG, utilizando-se as ferramentas CADENCE. Além disso, uma meta bastante importante desse projeto é a formação de recursos humanos de alunos de iniciação científica, mestrado e doutorado na área de projetos, simulação, leiaute e fabricação de circuitos integrados utilizando-se as ferramentas da CADENCE.

This work proposes a new technique and hardware architecture for control of multitasking in real-time systems (RTS) developed to run on single-core microprocessors or microcontrollers. It has as one of its objectives to implement automatically layouts of one digital processor based on VHDL/VERILOG files with the use of CADENCE EDA tools. Besides that, other very important goal of this project is the generation of human resources regarding scientific students, master students and PhD students in the design/simulation/layout/manufacturing of integrated circuits using CADENCE EDA tools.

Um aluno de Doutorado (LEANDRO POLONI DANTAS) e um aluno de iniciação científica (YURI GABRIEL DORGAN IASBECH) trabalharam com as ferramentas CADENCE para a geração automática de leiaute de um microprocessador MIPS modificado, conforme ilustrado na Figura 1.

One PhD Student (LEANDRO POLONI DANTAS) and one scientific student (YURI GABRIEL DORGAN IASBECH) work with the CADENCE tools to generate automatically the layout of a modified MIPS processor, as illustrated in Figure 1.

Figura 1. Arquitetura do processador MIPS modificado.

O aluno de doutorado, LEANDRO POLONI DANTAS, continua trabalhando no projeto de um microcontrolador MIPS modificado, no qual ele está incorporando um sistema operacional de tempo real (Real-Time Operational System, RTOS).

The PhD Student, LEANDRO POLONI DANTAS, continues working to design a modified MIPS microcontroller, which he is incorporating a real-time operational system (RTOS).

A Figura 1 ilustra o leiaute final do circuito do microcontrolador IHM-Plasma, com destaque para suas dimensões e área.

Figure 2 illustrates the final layout of the IHM-Plasma microcontroller implemented by using the Cadence tools.

Fonte: Autor

Figura 2 – Leiaute do microcontrolador IHM-Plasma.

Figure 2 – Layout of the IHM-Plasma microcontroller.

The Leandro Poloni Dantas will defende his PhD on May, 24 2018.

O aluno de iniciação científica (YURI GABRIEL DORGAN IASBECH) finalizou com sucesso o seu projeto de pesquisa, no qual leiautes de circuito integrado (CI) digitais podem ser gerados automaticamente através do uso das seguintes ferramentas: Quartus II (Verilog/VHDL) e da CADENCE (RTL Compiler e Encounter). Projeto finalizado em Dezembro de 2016.

The scientific student, YURI GABRIEL DORGAN IASBECH, finished with success his research project, which layouts of digital integrated circuits (ICs) can be generated automatically through the use of the following software tools: Quartus II (Verilog/VHDL) and CADENCE (RTL Compiler e Encounter). This project was finished in 2016 (December).

IGOR KRAUSE foi um aluno de iniciação cientifica e finalizou o seu projeto que foi um decodificador de 3 entradas e 8 saídas (Verilog/VHDL) e fez a geração automática desse leiaute utilizando-se as ferramentas da CADENCE, conforme pode ser visualizado na Figura 3. Finalizado em 2017.

IGOR KRAUSE was a scientific initiation student and he finished a project of a decoder with 3 inputs and 8 outputs (Verilog/VHDL) and implemented its layout by using the CADENCE tools, according Figure 3. Finalized in 2017.

Fonte: Autor

Figura 3 - Leiaute final do decodificador

Figure 3 – Final layout of the decoder

LUIS BINI foi um aluno de iniciação cientifica e finalizou os seu projeto de pesquisa relacionado a um multiplexador de 4 entradas e 16 saídas (Verilog/VHDL) e também implementou o leiaute desse projeto de forma automática utilizando-se as ferramentas da CADENCE, conforme pode ser visto na Figura 4. Finalizado em 2017.

LUIS BINI is another scientific initiation student and he finished his design of a multiplexer (mux) with 4 inputs and 16 outputs (Verilog/VHDL) and implemented its layout by using the CADENCE tools. Finished in 2017.

Fonte: Autor

Figura 4 - Leiaute final do multiplexador

Figure 4 – Final layout of the multiplexer

Outros estudantes irão continuar a ser treinados com as ferramentas da CADENCE a fim de projetarem circuitos integrados no Centro Universitário FEI.

Others students will continue being trained with the CADENCE tools in order to design integrated circuits at FEI University Center (Centro Universitário FEI).

O Centro Universitário FEI reconhece CADENCE pela oportunidade de participar do Programa Universitário.

FEI University Center acknowledges CADENCE by the opportunity to participate of the University Program.

Projeto iniciado em 2016 e em andamento.

Project started in 2016 and ongoing.

Project: The next generation of non-standard layout styles for MOSFETs.

Prof. Dr. Salvador Pinillos Gimenez

The non-standard gate geometries [Hexagonal/Diamond, Octagonal: Octo, Ellipsoidal, Wave, Overlapping-Circular Gate (O-CGT), and Fish] for MOSFETs are capable of booting their electrical performance and the ionizing radiation tolerance simultaneously in comparison to those found in standard gate geometries (rectangular) MOSFETs counterparts, whose were already published in international journals and congresses. This happens due to the presence of the new effects in their structures already reported in the literature, such as the Longitudinal Corner Effect (LCE): responsible for boosting the resultant longitudinal electric field due to the drain to source bias in comparison to the one measured in the Rectangular MOSFET counterpart (same gate area, channel width, and bias conditions); PArallel connections of MOSFETs with Different Channel Lengths (L) Effect (PAMDLE): responsible for reducing the effective channel length (Leff) in relation to the one measured in the Rectangular MOSFET counterpart (same gate area and channel width); Deactivation of the Parasitic MOSFET in the Bird's Beak Regions Effect (DEPAMBBRE): responsible for curving the resultant longitudinal electric field along of the channel length of the MOSFET and consequently electrically deactivating the parasitic MOSFETs of the Bird's Beak regions [1-19].

In this context, I am proposing a new line of non-orthodoxy layout styles for MOSFETs which are more effectives and are able to further improving the electrical performance and the ionizing radiation tolerances of MOSFETs. These innovative layout styles are based in the hexagonal, octagonal, ellipsoidal, etc., but they present smaller dimensions in relation to the Diamond, Octo, and Ellipsoidal layout styles for MOSFETs already studied by my research group. Besides, I will study the electrical behavior of these new layout styles in comparison to the conventional (rectangular) MOSFETs. Furthermore, I will use them as unit (base) cells to implement Planar Power MOSFETs (parallel association of MOSFETs) which their electrical behavior will be compared to those of the multifinger (rectangular) Power Planar MOSFETs.

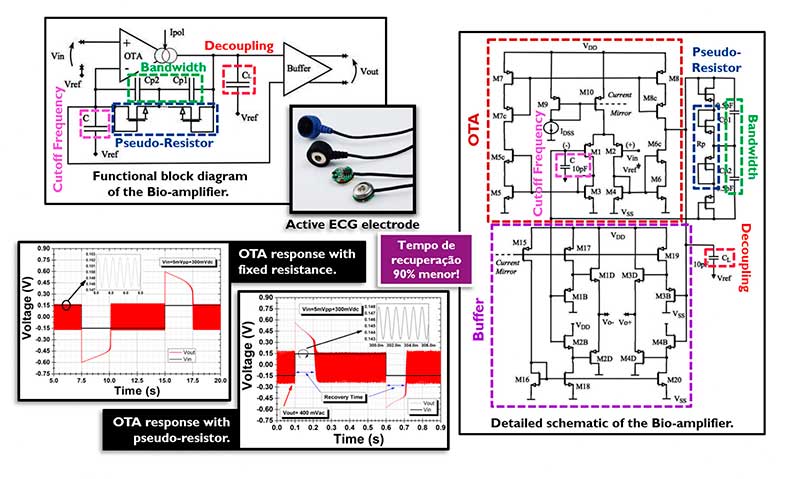

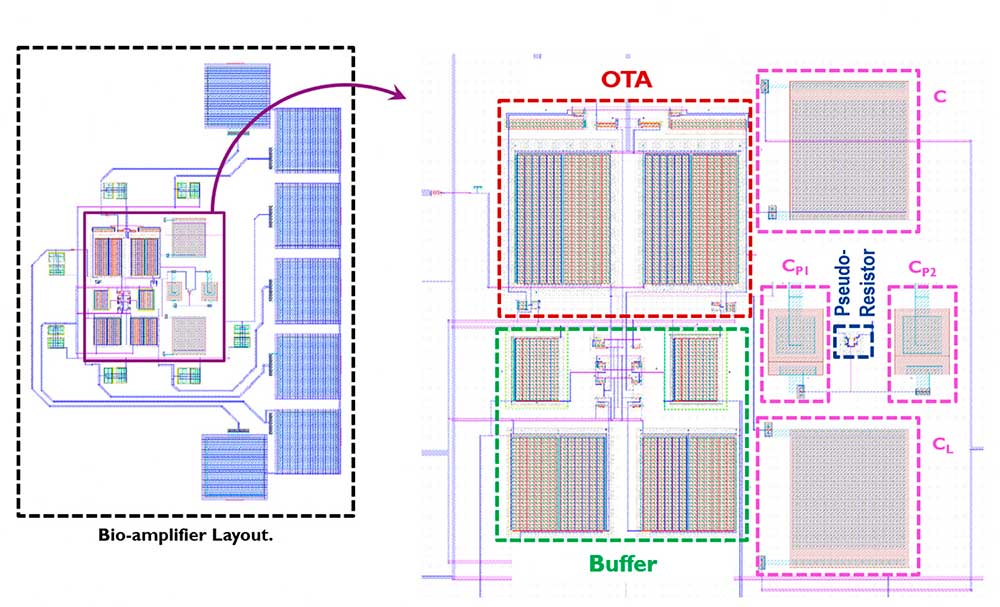

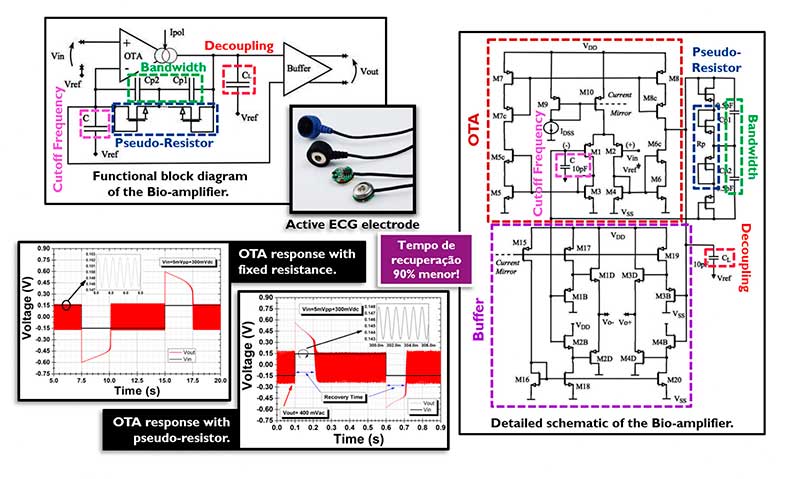

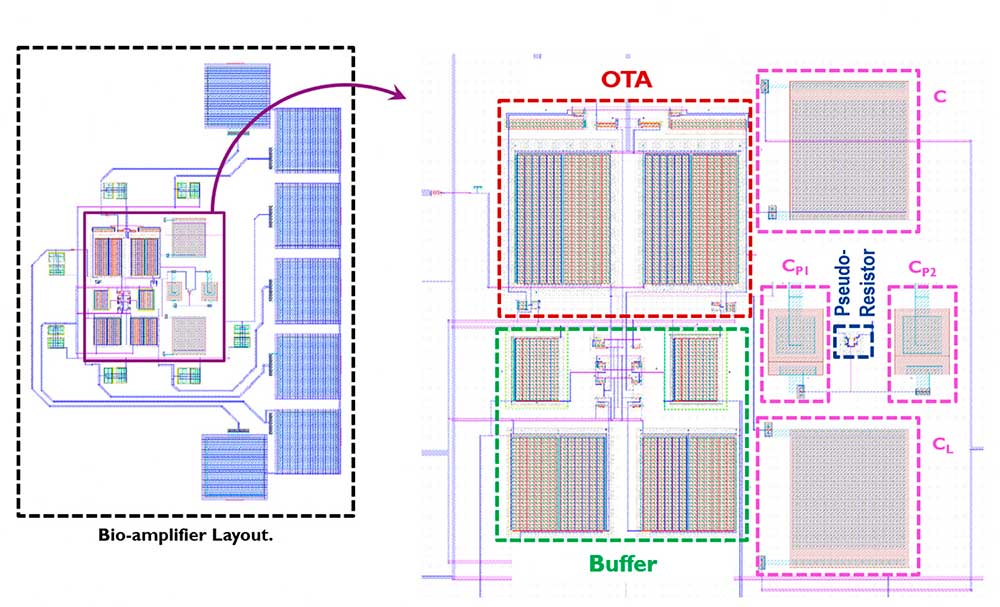

Projeto: Novo Amplificador de Bio-Potencial Utilizando Pseudo-Resistor Bipolar-MOS com Baixa Impedância de Saída Diferencial

Prof. Dr. Renato C. Giacomini

A aquisição de sinais bioelétricos tem sido um desafio para os designers eletrônicos. Os sinais elétricos de baixo nível adquiridos pelos transdutores de eletrodos (de décadas de µV a alguns mV) estão associados a umacomponente intrínseca de CC criada pela associação eletrodo-eletrólito, que varia de 100 a 500 mV. Estes sinais são conectados através de um longo caminho para a entrada do amplificador (cabos, conectores), resultando em um problema crítico, envolvendo cancelamento DC e baixa relação sinal/ruído. Algumas soluções foram apresentadas em artigos utilisando o pseudo-resistor bipolar MOS com diferentes tecnologias e soluções de circuitos. Outros trabalhos com foco no pseudo-resistor foram publicados, para diferentes tecnologias (1,5µm; 0,5µm e 0.18µm), mostrando que as aplicações ainda estão em pesquisa, mas nenhuma na tecnologia BiCMOS de 0,13µm.

Este projeto pretende implementar uma nova topologia de bio-amplificador, partindo de resultados anteriores, obtidos a partir de circuitos anteriores, fabricados pela MOSIS na tecnologia BiCMOS 8HP 0,13µm. O amplificador utiliza pseudo-resistores bipolares MOS.

Situação atual: Foram produzidos amplificadores para deteção das ondas QRS, que estão em testes de laboratório. Na próxima rodada, serao produzidos circuitos completes dos amplificadores.

Project: Design of a New Bio-potential Amplifier Using MOS-Bipolar Pseudo-Resistor with Differential Low Output Impedance

Prof. Renato C. Giacomini, PhD

Bioelectric signal acquisition has been a challenge to electronic designers. The low-level electric signals acquired by the electrode transducers (from decades of µV, to some mV) are associated with an intrinsic DC component created by the electrode-electrolyte association, which ranges from 100 to 500mV. These signals are connected through a long path to the amplifier input (cables, connectors), resulting in a critical problem, involving DC cancellation and low signal-to-noise ratio. Some solutions have been presented in papers using the MOS-bipolar pseudo-resistor with different technologies and circuit solutions. Other works with focus on the pseudo-resistor were published, for different technologies (1.5µm, 0.5µm, and 0.18µm), showing that applications are still being researched, but no one with 0.13µm technologies in BiCMOS.

The present project intends to implement a new bio-amplifier topology, departing from previous results, obtained from partial circuits, which were assembled by MOSIS in BiCMOS 8HP 0.13µm last year. The amplifier uses MOS-bipolar pseudo-resistors.

Current situation: Some amplifiers were produced for QRS wave detection, which are in lab tests. In the next run, complete amplifier circuits will be produced.

Projeto: Modulador Chaveado de Amplitude SubGHz

Prof. Dr. Renato C. Giacomini

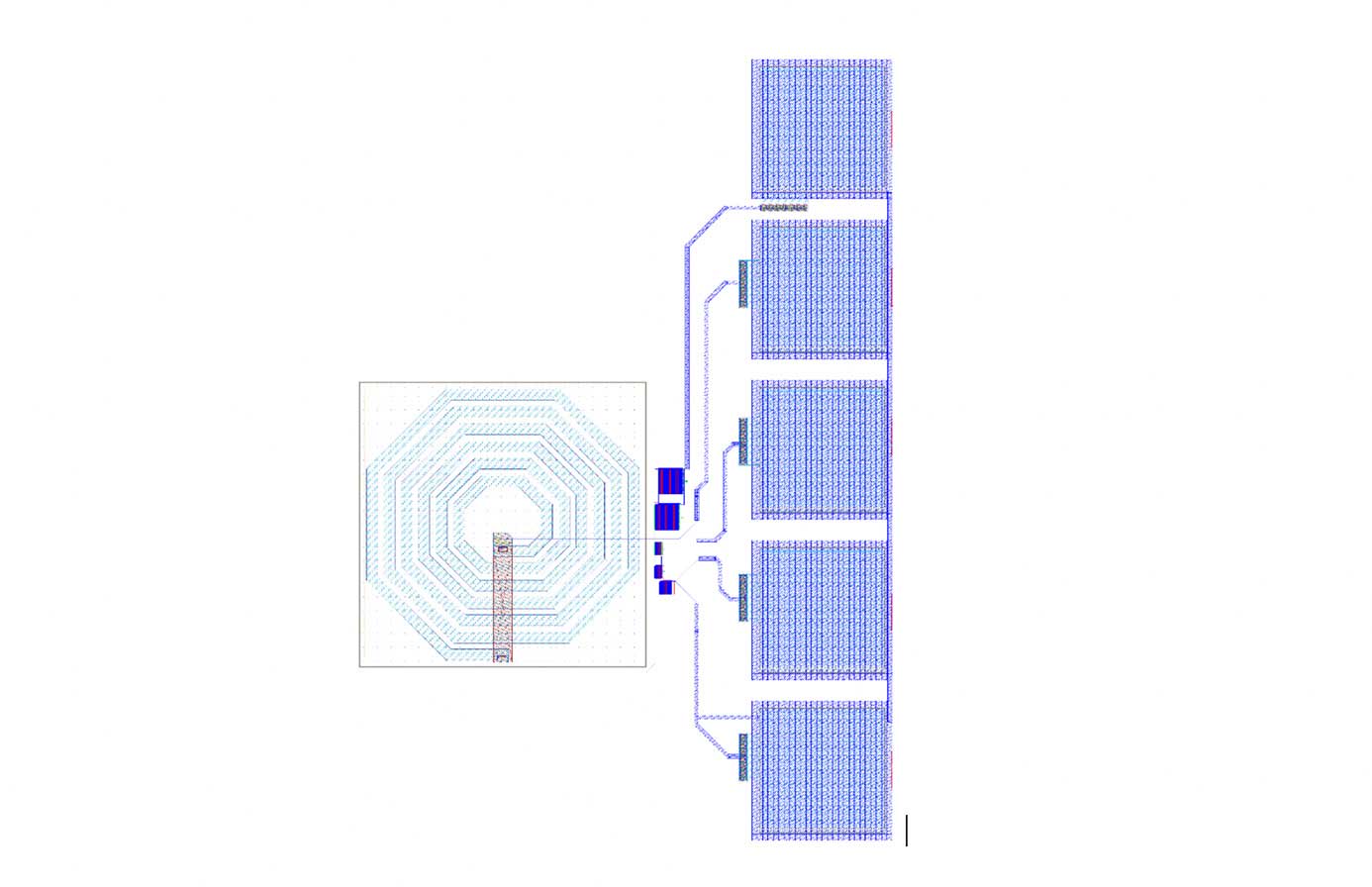

Este projeto implementa um modulador de modulação de amplitude Shift Keying – ASK usando a topologia Complementary Cross-Coupled LC Oscillator. São utilizados transistores nMOS e pMOS. A modulação está na faixa RF de 1GHz. O consumo de energia é de 10mW e VDC 2.5V. O indutor é implementado através de uma bobina.

No momento está em projeto uma nova versão, com amplificadores acoplados à saída de sinal.

Project: SubGHz Amplitude Shift Keying Modulator

Prof. Renato C. Giacomini, PhD

This project implements an Amplitude Shift Keying – ASK modulator using the Complementary Cross-Coupled LC Oscillator topology. Both nMOS and pMOS transistors are used. The modulation is in Sub 1GHz RF range. The power consumption of 10mW and VDC 2.5V. The inductor is implemented through a coil.

At the moment a new version is being designed, with amplifiers coupled to the signal outputs.

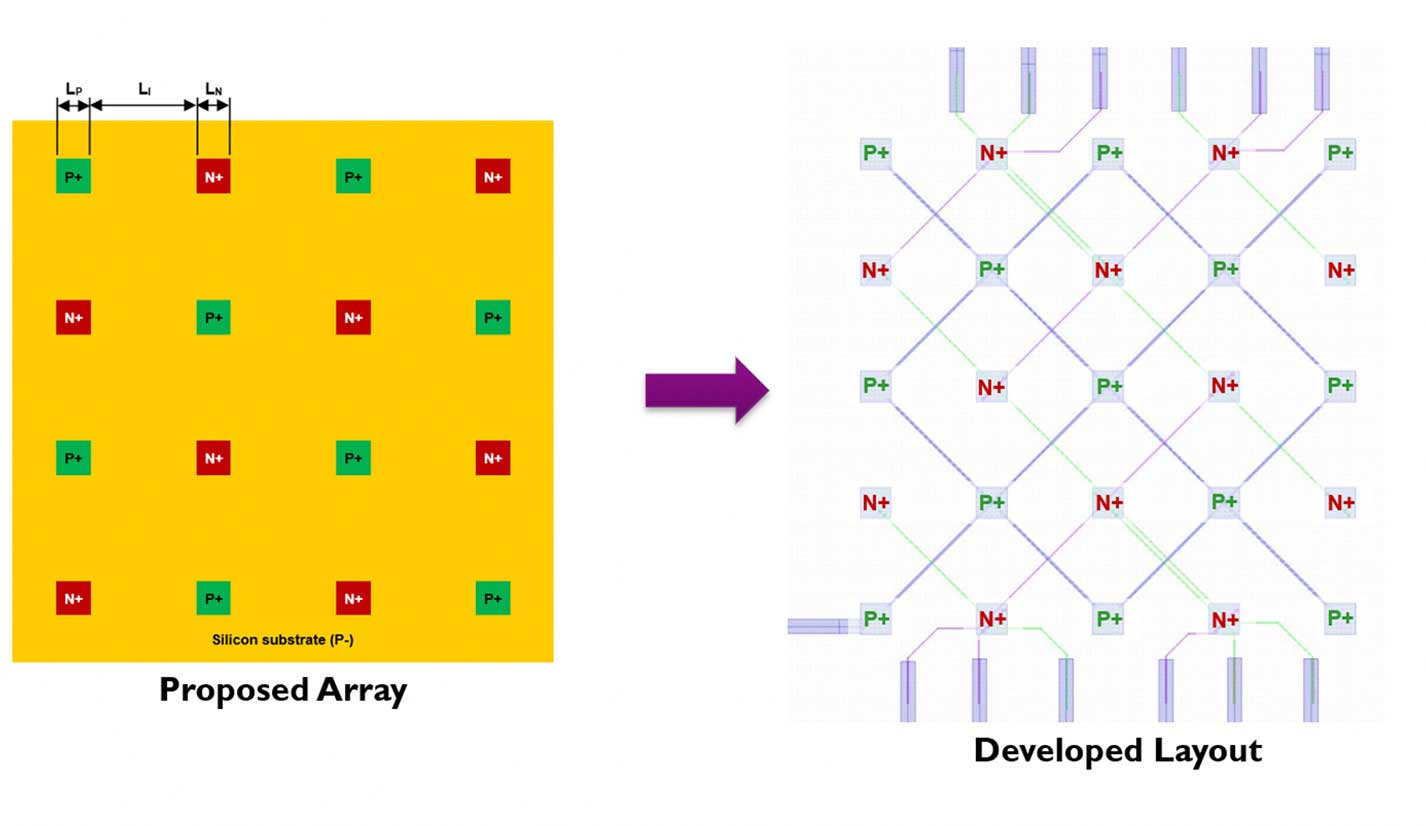

Projeto: Matriz para Discriminação de Comprimento de Onda com diodos PIN Laterais

Prof. Renato C Giacomini, PhD;

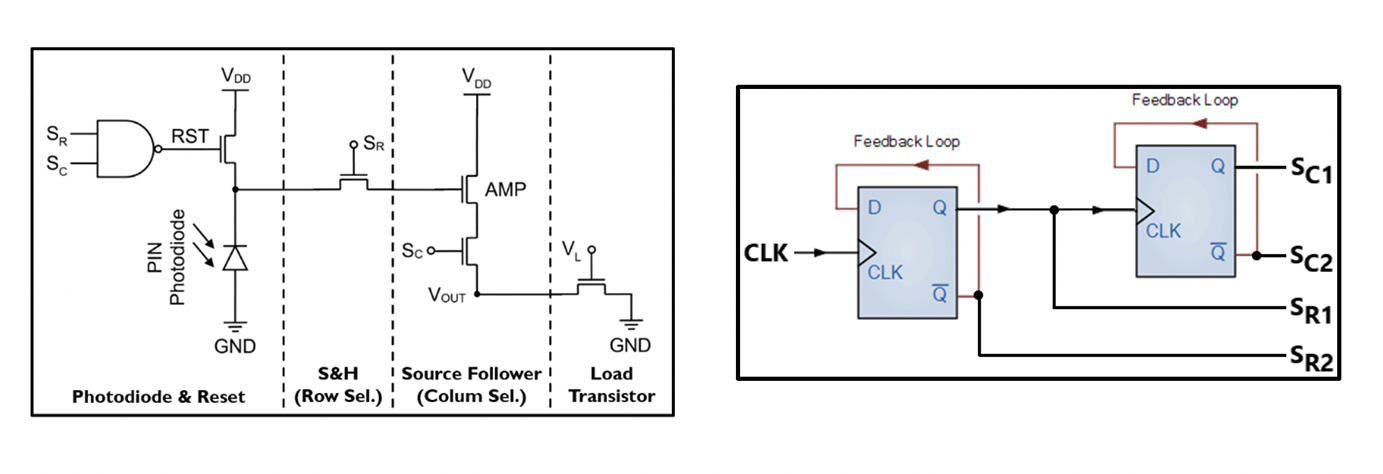

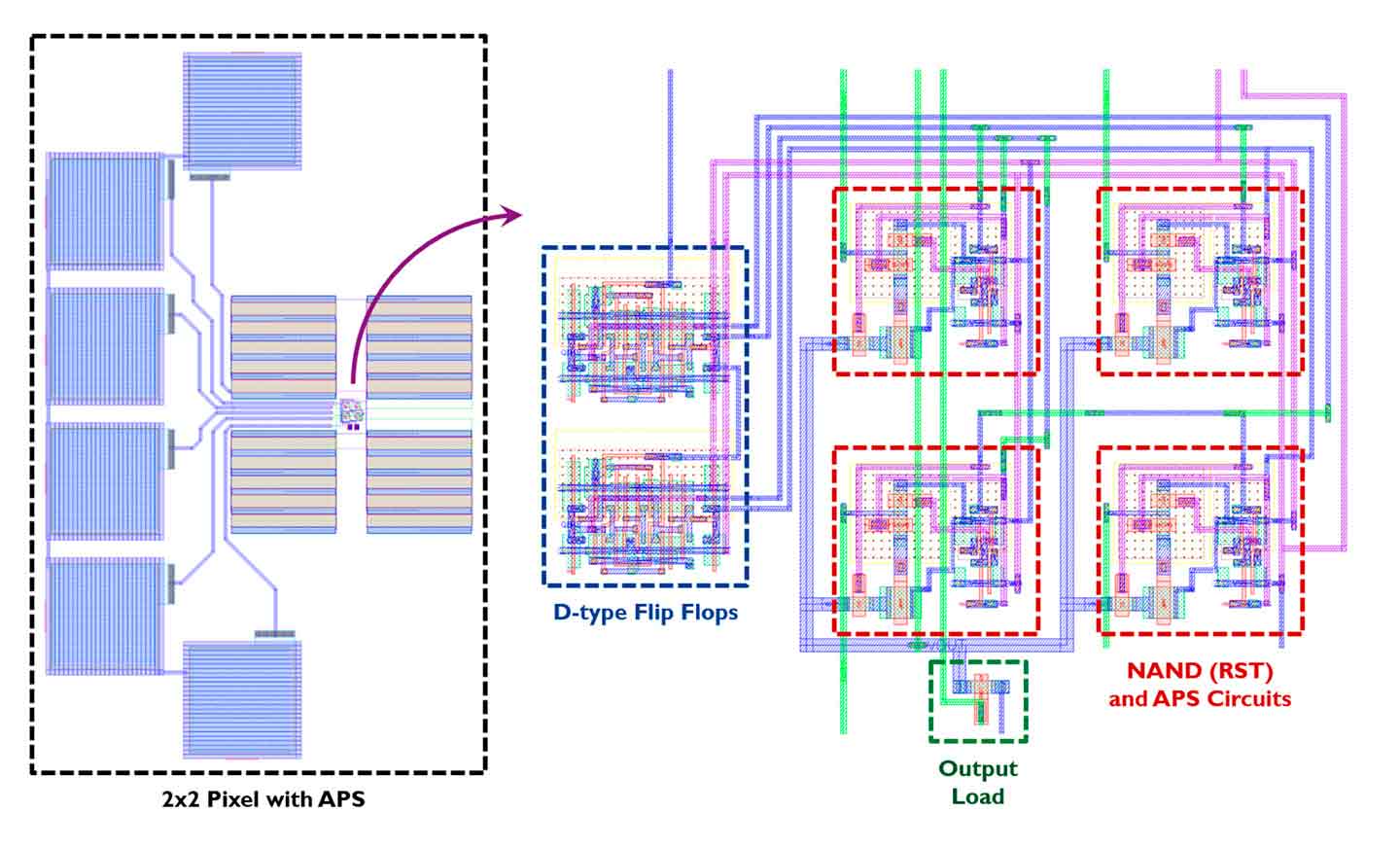

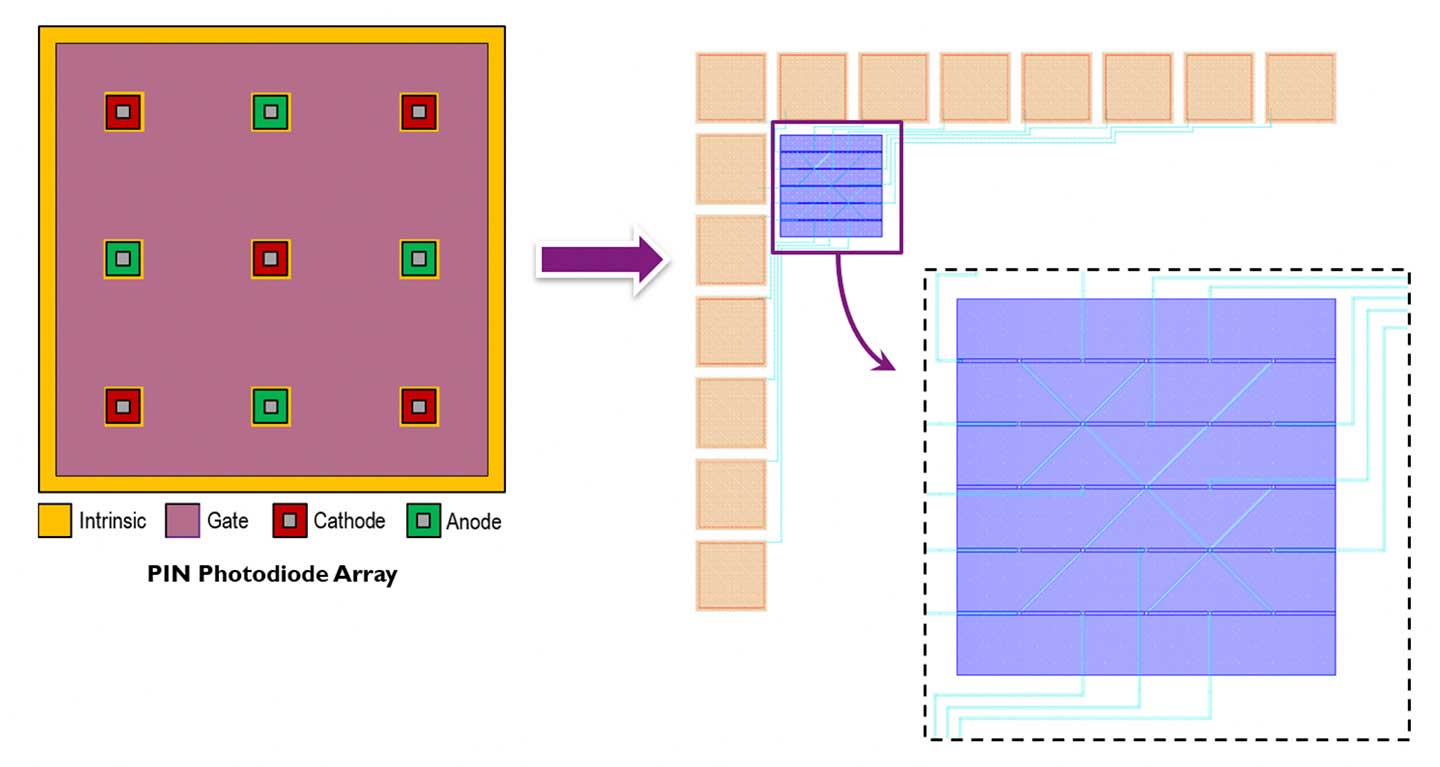

Prof. Rudolf, T Buhler, PhD

O conceito de diodos PIN laterais apresentado na figura 1 (a) é usado para implementar uma matriz (figura 1 b) que discriminará os comprimentos de onda de luz. O circuito APS (active pixel sensor) é apresentado na figura 1 (c), formado por 1 fotodíodo PIN, 1 transistor MOS para reset (RST), 2 transistores MOS para seleção de linha e coluna (SR e SC, respectivamente), 1 MOS transistor para amplificação de sinal (AMP), terminais de alimentação (VDD e GND) e o sinal de saída (VOUT). Os transistores SR e SC operarão em regime triodo (linear). O circuito APS será inserido em cada cátodo, conforme apresentado na figura 1 (d), e coberto por metal. Os dados recolhidos serão posteriormente analisados através de análise de discriminação linear.

Project: Wavelength Discriminant Lateral Gated PIN Diode Matrix

Prof. Renato C Giacomini, PhD;

Prof. Rudolf, T Buhler, PhD

The concept of lateral gated PIN diodes presented in figure 1 (a) are used to implement a matrix (figure 1 b) that will discriminate wavelengths. The APS circuit (a.k.a. PIN Cell) is presented in figure 1 (c), formed by 1 PIN photodiode, 1 MOS transistor for reset (RST), 2 MOS transistors for row and column selection (SR and SC, respectively), 1 MOS transistor for signal amplification (AMP), power supply terminals (VDD and GND) and the output signal (VOUT). The SR and SC transistors will operate in triode (linear) regime. The APS circuit will be insert in each cathode, as presented in figure 1 (d), and covered by metal. The gathered data will be latter analyzed through linear discrimination analysis.

(A)

(A)

(B)

(B)

(C)

(C)

(D)

(D)

Figure 1 – Basic schematic view of (a) a single lateral PIN diode, (b) the matrix structure, (c) APS circuit and (d) PIN cell inside the cathode.

Projeto: Amplificador de Bio- Potencial Utilizando Pseudo-Resistor Bipolar-MOS com Baixa Impedância de SaídaDiferencial e curto tempo de Recuperação

Prof. Renato C Giacomini, PhD;

A aquisição de sinais bioelétricos tem sido um desafio para os designers eletrônicos. Os sinais elétricos de baixo nível adquiridos pelos transdutores de eletrodos (de décadas de µV a alguns mV) estão associados a umacomponente intrínseca de corrente contínua criada pela associação eletrodo-eletrólito, que varia de 100 a 500 mV. Estes sinais são conectados através de um longo caminho para a entrada do amplificador (cabos, conectores), resultando em um problema crítico, envolvendo cancelamento DC e baixa relação sinal/ruído. Algumas soluções foram apresentadas em artigos utilizando o pseudo-resistor bipolar MOS com diferentes tecnologias e soluções de circuitos. Outros trabalhos com foco no pseudo-resistor foram publicados, para diferentes tecnologias (1,5µm; 0,5µm e 0.18µm), mostrando que as aplicações ainda estão em pesquisa, mas nenhuma na tecnologia BiCMOS de 0,13µm.

Este projeto implementa uma nova topologia de bio-amplificador, partindo de resultados anteriores, obtidos a partir de circuitos anteriores, fabricados pela MOSIS na tecnologia BiCMOS 8HP 0,13µm. O amplificador utilizapseudo-resistores bipolares MOS.

Foram projetados e fabricados amplificadores para detecção das ondas QRS, que estão em testes de laboratório.

Project: The "Second Generation" of Non-Standard layout styles for MOSFETs. 2x2

Prof. Dr. Salvador Pinillos Gimenez

Several publications on journals and international congresses have shown that the non-standard gate geometries [Hexagonal/Diamond, Octagonal: Octo, Ellipsoidal, Wave, Overlapping-Circular Gate (O-CGT), and Fish] for MOSFETs are capable of booting their electrical performance due to the LCE and PAMDLE effects, and the ionizing radiation tolerance due to the DEPAMBBRE effect, simultaneously, in comparison to those found in standard gate geometries (rectangular) MOSFETs counterparts [1-19].

In this context, I have manufactured several MOSFETs with the non-standard gate geometries (Half-Diamond MOSFETs, Half-Octo MOSFET, and Half-Ellipsoidal MOSFETs) of the "Second Generation" of innovative layout styles for MOSFETs by using the 180 nm Bulk CMOS ICs technology from TSMC. The main characteristics of these MOSFETs is that they present smaller channel lengths of the "First Generation" (Diamond MOSFET, Octo MOSFET and Ellipsoidal MOSFETs) and consequently the LCE and PAMDLE effects in the MOSFETs of the "Second Generation" tend to be more intensive than those observed in the First Generation and therefore these innovative layout styles for MOSFETs can further improve their electrical performance and further reduce the die area of these devices and of the analog and radio-frequency CMOS ICs, as illustrated in Fig bellow.

Besides, the MOSFETs manufactured with the innovative layouts styles of the "Second Generation" continue to present the DEPAMBBRE effect and consequently they will continue to present improved "Total Ionizing Dose" (TID) tolerances than those observed in the standard MOSFETs.

These innovative MOSFETs with the "Second Generation" have been studying by experimental data by me and by my students (Scientific Initiation, Master and PHD) and their electrical behavior will be compared to the conventional (rectangular) MOSFETs and those of the "First Generation". Furthermore, I will use them as unit (base) cells to implement Planar Power MOSFETs (parallel association of MOSFETs) which their electrical behavior will be compared to those of the multifinger (rectangular) Power Planar MOSFETs.

Project: Differential Bio-Amplifier Circuit for Bio-Signals

Prof. Dr. Renato C. Giacomini

A differential bio-amplifier circuit using the pseudo-resistor previously proposed. The pseudoresistor is used in the feedback network of bio-amplifiers to eliminate low frequencies and DC levels that can disturb the bio-potential acquisition. The use of pseudo-resistor sets the lower-cutoff frequency with the advantage of using smaller die area when compared to regular resistors and allows faster recovery times.

Basic schematic view of the lateral gated PIN diode frequency sensor.

Current status: In the development phase, the circuit will be produced.

Project: Bio-Potential Amplifier Using Bipolar-MOS Pseudo-Resistor with Low Differential Output Impedance and Short Recovery Time

Prof. Renato C Giacomini, PhD;

The acquisition of bioelectric signals has been a challenge for electronic designers. The low-level electrical signals acquired by electrode transducers (from decades of µV to some mV) are associated with an intrinsic component of direct current created by the electrode-electrolyte association, which varies from 100 to 500 mV. These signals are connected through a long path to the amplifier input (cables, connectors), resulting in a critical problem, involving DC cancellation and low signal / noise ratio. Some solutions were presented in articles using the bipolar MOS pseudo-resistor with different technologies and circuit solutions. Other works focusing on the pseudo-resistor have been published, for different technologies (1.5µm; 0.5µm and 0.18µm), showing that the applications are still in research, but none in the 0.13µm BiCMOS technology.

This project implements a new bio-amplifier topology, based on previous results, obtained from previous circuits, manufactured by MOSIS using BiCMOS 8HP 0.13µm technology. The amplifier uses bipolar MOS pseudo-resistors.

Amplifiers were designed and manufactured to detect QRS waves, which are in laboratory tests.

Current status: Amplifiers were produced to detect QRS waves, which are in laboratory tests. In the next round, complete circuits of the amplifiers will be produced.

Project: Pseudo-Resistor structures without external polarization of door

Prof. Dr. Renato C. Giacomini

With a focus on the evolution of bio-potential amplifiers, new pseudo-resistor topologies were designed and sent for manufacturing. A model implemented in SPICE is in the final stage of implementation and new experimental data from these devices will assist in its development.

Current status: New pseudo-resistors are being manufactured for the evolution and development of the SPICE model.

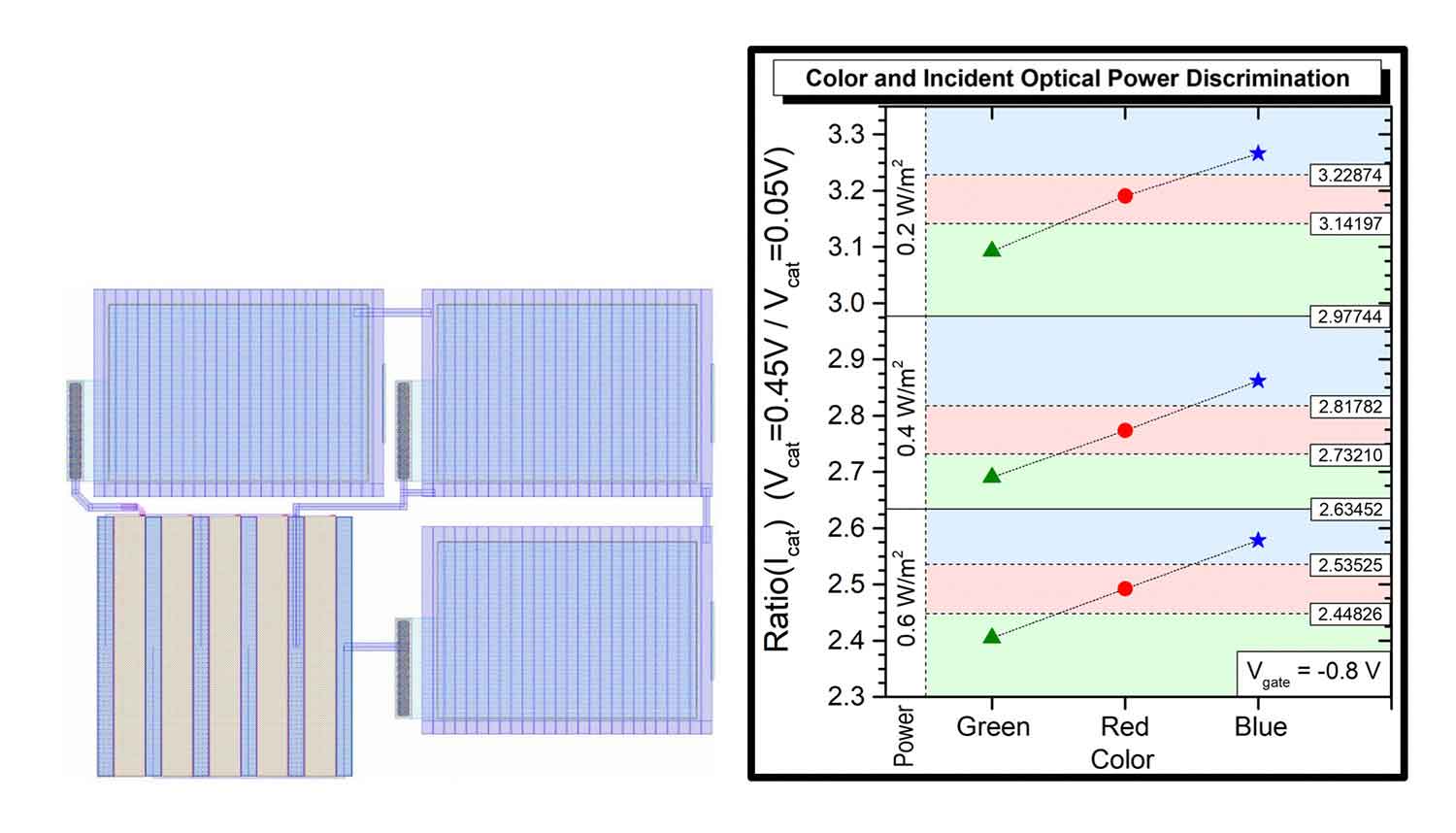

Project: Discrimination of wavelengths and optical power in a 2x2 Pixel sensor

Prof. Renato C Giacomini, PhD;

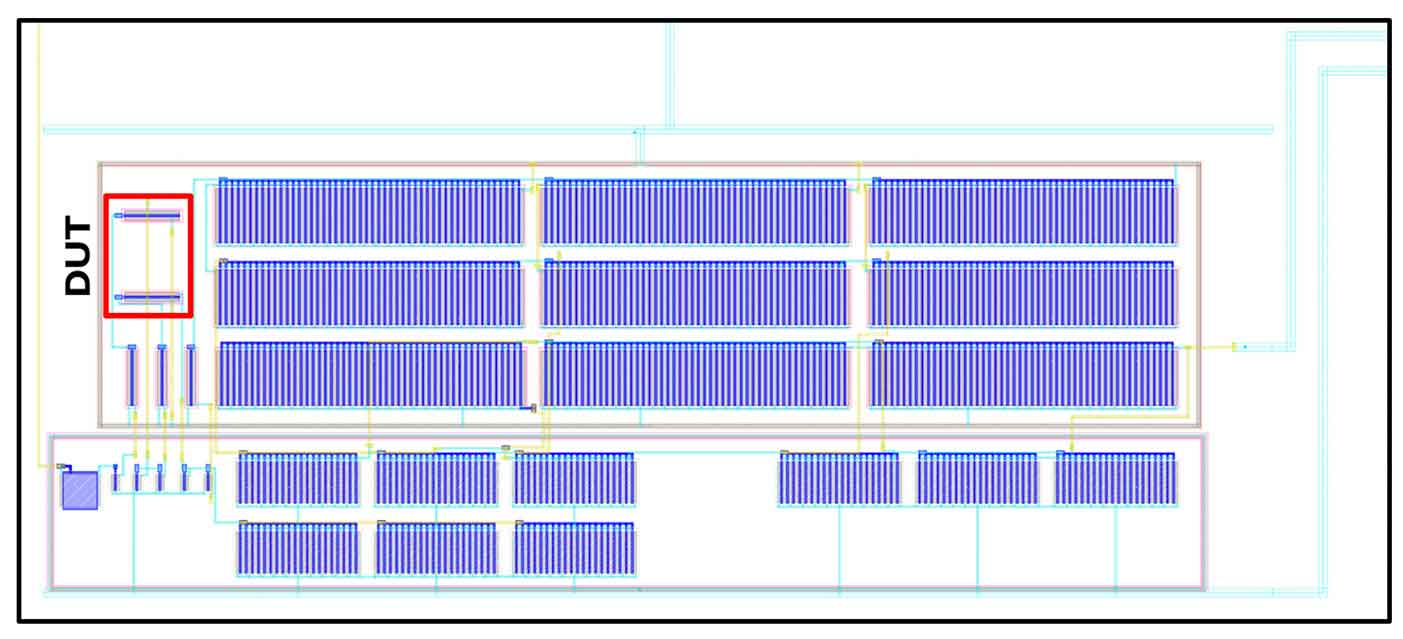

The lateral PIN photodiodes with door and multidedos, manufactured through the agreement with MOSIS and IMEC, and shown in the following figure was developed to discriminate conda lengths of the RGB light spectrum with multiple light intensities.

Use of a reset APS circuit to sample and maintain and amplify the photocurrent, in a 2x2 Configuration for the acquisition of the photocurrent level and a line / column selection circuit composed of 2 type D Flip-Flops.

Full layout developed:

The same concept of PIN photodiodes with side door as before is used to implement a matrix that will discriminate wavelengths and light intensity:

Current status: Circuits for detecting wavelengths were produced. Electrical characterizations will be performed.

Project: Finite State Machine (FSM) capable of recovering after an electromagnetic interference

Prof. Renato C Giacomini, PhD;

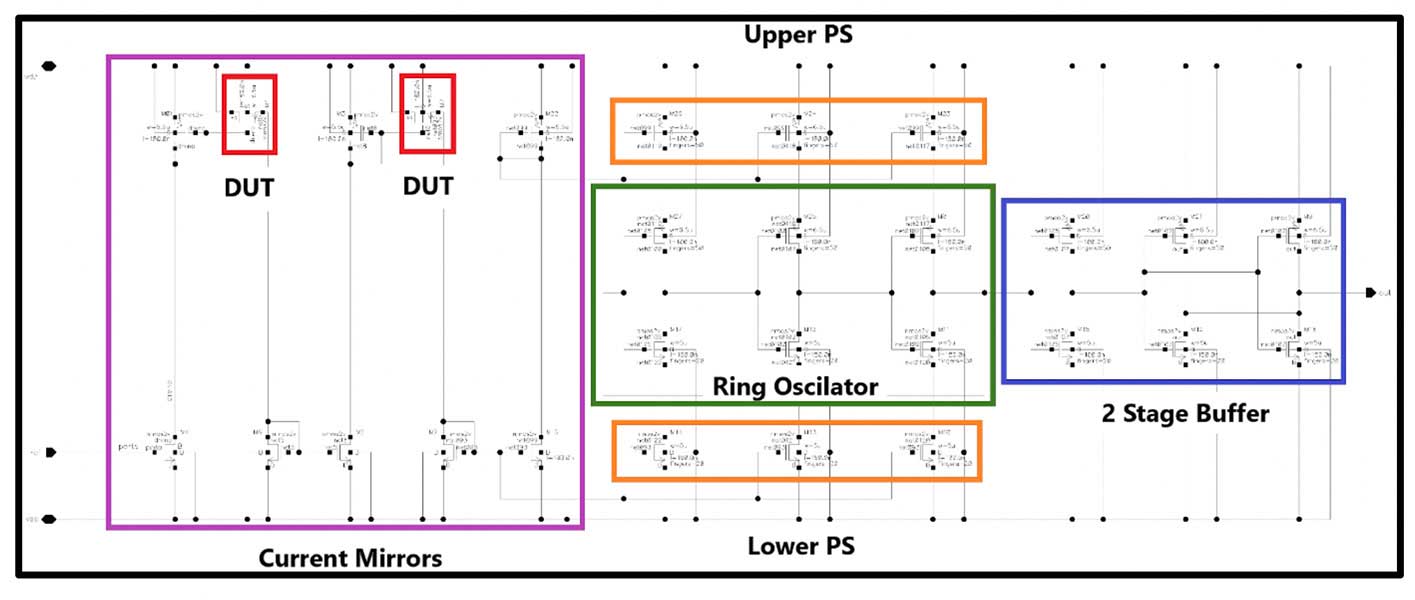

The objective of this proposal is the fabrication of a semiconductor device for study and evaluation of digital architecture techniques. These techniques were studied during the master's degree course and were subject for a dissertation. The study focused in means to build a Finite State Machine (FSM) capable of recovering after an electromagnetic interference, as a power supply noise, that could change the state of a flip-flop. The proposed device shall be composed of two FSM and an interface hardware to support the tests and verifications.

In the device, one FSM shall use the studied digital architecture techniques and the second shall be build using conventional digital circuitry. The interface logic will provide the data input and output for the FSMs, as well as a glitch detector to record the error events. The interface is also useful to reduce the external pin count, handling all data serially.

The device shall use around 12,000 transistors and 7 pads for power supply and interface signals. The figure below illustrates the structure of the device.

The glitch detectors are a new design motivated to build a library of reliable digital test circuits that can be used in other ICs. This can be an important tool for students to verify their designs using simple serial interface, similar, but not equal, to the well-known JTAG. The error event capture registers shall be doubled to enable the detection of an error in the capture registers. The valid errors, detected from state machines, must appear in both capture registers.

The serial interface enables low pad count. This design will use 4 pads for serial interface and 3 pads for power supply. The serial interface, I/O registers and Capture registers shall use a unique power supply line, while the FSMs will use a separate one. This allows noise injection in the FSM power supply and keep clean the power for the interface circuit.

The libraries generated by this work shall be made available for other students to use in their designs.

Current status: In the development phase, the circuit will be produced.

Project: Sensing of mechanical deformations

Prof. Renato C. Giacomini, PhD

Circuit developed to analyze the induced mechanical stress, in the frequency domain:

And its respective layout:

Current status: Circuit designed and manufactured. Electrical characterizations will be performed.

Project: SubGHz Amplitude Modulator Shift Keying

Prof. Renato C. Giacomini, PhD

This project implements an Amplitude Shift Keying (ASK) modulator using the Complementary Cross-Coupled LC Oscillator topology. Both nMOS and pMOS transistors are used. The modulation is in the Sub 1GHz RF band with power consumption of 10mW and VDC of 2.5V. The inductor is implemented through a coil.

Current status: A new version is being designed, with amplifiers coupled to the signal outputs.

Project: Sensing the Effects of Unique Particle Radiation Events (SEE)

Prof. Renato C. Giacomini, PhD

Heavy ion radiation interferes with the response of the device, causing it to malfunction. Developed in partnership with the CITAR Project, the Single Event Effects detection matrix is presented below, manufactured using GF BiCMOS 8HP 0.13 technology:

Current status: Circuit designed and manufactured. Electrical characterizations will be performed.

Cadence is a registered trademark of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134.

Last updated: May 21, 2020. Copyright of these papers, reproduced here for timely dissemination of research information, is with the respective publishers.

Nanoeletrônica e Circuitos Integrados

Uma das áreas mais importantes dentro da Engenharia Elétrica é a área de Nanoeletrônica e Circuitos Integrados. Essa área vem recebendo os mais altos níveis de investimentos mundiais. Ela é considerada a base para as demais ciências e é responsável por fornecer os insumos básicos (circuitos integrados) para a fabricação de equipamentos eletrônicos das mais diversas áreas do conhecimento, objetivando a melhoria da qualidade de vida do ser humano.

O desenvolvimento da área de Nanoeletrônica constitui atualmente uma das maiores preocupações da sociedade brasileira, pois observa-se um crescente déficit na balança comercial decorrente da importação de componentes eletrônicos para a fabricação de diversos equipamentos de interesse, tais como equipamentos eletrônicos embarcados (carro, trem, navio, avião e aeronave espacial), médicos (marca-passo e ressonância magnética), de comunicações analógica e digital (telefone celular e intercomunicador), de automação residencial, predial e industrial (alarme, controlador de elevador e robô), entretenimento (videogame, rádio e televisão digital) e computadores pessoais e industriais. Uma das razões para a não existência de empresas nacionais nesta área é a pequena quantidade de profissionais com formação especializada, capazes de atuar neste ramo industrial.

Dentro deste contexto, os cursos de Mestrado e Doutorado propostos visam permitir que engenheiros e profissionais de áreas afins busquem capacitação em nível de pós-graduação stricto-sensu na área de Nanoeletrônica, com especial ênfase para as linhas de pesquisa em caracterização elétrica de dispositivos eletrônicos, simulação e modelagem analítica de dispositivos eletrônicos, e projeto de circuitos integrados dedicados, melhorando a qualidade da mão-de-obra nacional nestas áreas de concentração e dando suporte ao surgimento de empresas de pequeno porte especializadas no projeto de circuitos integrados. Os profissionais voltados para estudos de falhas em circuitos eletrônicos podem também se beneficiar do programa de pós-graduação proposto, uma vez que o mesmo possui como uma de suas áreas principais a caracterização elétrica de componentes eletrônicos, permitindo a identificação de falhas e o estudo detalhado das componentes físicas que originaram a falha.

Linhas de Pesquisa

Nesta linha de pesquisa são estudadas as propriedades elétricas de dispositivos eletrônicos, especialmente os fabricados na tecnologia de Metal-Óxido-Semicondutor (MOS) de dimensões nanométricas. Estes estudos são realizados através de medidas elétricas estáticas (do tipo corrente-tensão), dinâmicas (do tipo capacitância-tensão), pulsadas e de ruído de baixa frequência. As medidas elétricas são também realizadas em função da temperatura e sob efeitos de radiação, avaliando a influência das condições do ambiente sobre as propriedades elétricas dos componentes eletrônicos.

Nesta linha de pesquisa, simuladores numéricos bidimensionais e tridimensionais de processos de fabricação e de dispositivos eletrônicos são utilizados para obtenção de propriedades elétricas de dispositivos nanoeletrônicos, explorando a possibilidade de alteração de variáveis intrínsecas dos dispositivos, tais como materiais, espessuras, temperatura, ambiente, presença ou não de radiação e campo magnético, além da proposta de novas arquiteturas de leiaute. O desenvolvimento de modelos analíticos para a descrição de propriedades elétricas de componentes eletrônicos constitui uma outra área dentro desta linha de pesquisa. Os resultados de simulação e modelagem são, geralmente, comparados aos obtidos pela linha de pesquisa de Caracterização Elétrica de Dispositivos Eletrônicos, promovendo sua contextualização e validação.

Nesta linha de pesquisa desenvolve-se o projeto de circuitos integrados dedicados, digitais e analógicos. Também estudam-se sensores incorporados aos circuitos integrados e seus sistemas eletrônicos de interface. Os circuitos desenvolvidos visam o aproveitamento das vantagens de dispositivos avançados, com melhorias de desempenho e redução do consumo de potência. Nesta linha de pesquisa também é realizada a avaliação experimental do desempenho dos circuitos integrados projetados.

Inteligência Artificial Aplicada à Automação e Robótica

Há uma crescente demanda por profissionais altamente qualificados nas áreas de automação, sistemas inteligentes e principalmente na área de robótica autônoma e móvel. A importância do desenvolvimento científico e da capacitação tecnológica nessas áreas fica evidente quando se analisa a necessidade crescente da sociedade e da indústria por robôs cada vez mais autônomos e inteligentes, e da automação de processos orientados por uma produção sob demanda. A área de concentração em Inteligência Artificial Aplicada à Automação e Robótica visa desenvolver competência e pesquisa científica em novas tecnologias nas seguintes áreas:

Linhas de Pesquisa

As áreas de aprendizado de máquina e raciocínio automático para tomada de decisões estão se tornando cada vez mais comuns nos novos desenvolvimentos tecnológicos, seja pela aplicação de técnicas tradicionais ou as novas tendências de Deep Learning. Nesta linha de pesquisa, enfatiza-se a investigação científica e o desenvolvimento de técnicas computacionais que englobem os seguintes tópicos: Representação de Conhecimento; Raciocínio Espacial; Raciocínio Qualitativo; Programação em Lógica; Redes Neurais Artificias e Deep Learning; Raciocínio Baseado em Casos; Visão Computacional; Aprendizado por Reforço; Representação do Conhecimento; Ontologia; Algoritmos Evolutivos e Bioinspirados; Robótica Cognitiva; Tomada de Decisões; Linguística Computacional; Modelagem de processos Markovianos e Redes Bayesianas.

A robótica móvel, autônoma e inteligente está se tornando cada vez mais influente e importante na sociedade atual. Seja para novos processos agrícolas, segurança, limpeza, saúde, transporte, interação com as pessoas ou até mesmo para entretenimento, a robótica móvel inteligente está transformando a sociedade que conhecemos. E para que esta transformação seja feita de forma adequada, pesquisas cientificas e avanços tecnológicos precisam ser desenvolvidos. Portanto, esta linha de pesquisa visa atuar nos seguintes tópicos: Interação Humano-Robô; Sistemas Colaborativos Inteligentes; Robótica Humanóide; Robótica Educacional; Robótica Móvel; Robótica Colaborativa; Sistemas Multi-robôs e distribuídos; Sistema heterogêneos; Veículos Autônomos Inteligentes.

As tecnologias inteligentes estão, a cada dia, mais próximas do ser humano, que de modo interativo, usa ou usufrui destes sistemas para resolver problemas ou atingir determinados objetivos. As pesquisas que envolvem a interação entre o homem e as máquinas (computadores, robôs, carros autônomos ou casas inteligentes) se tornam, portanto, cruciais para o desenvolvimento e o avanço dessas tecnologias para novos patamares onde as máquinas podem tomar decisões ou atuarem junto com o ser humano em seu dia-a-dia. Com isso, esta linha de pesquisa tem como foco o desenvolvimento de metodologias, técnicas, modelos e algoritmos nos seguintes tópicos: Interação humano-Computador; Interface Adaptativa; Interface Cérebro-Computador; Planejamento; Automação Residencial e Predial inteligente; Sistemas Autônomos; Internet das Coisas (IOT).

Processamento de Sinais e Imagens

Com os avanços tecnológicos em diversas áreas do conhecimento humano, há uma necessidade cada vez maior de representar, extrair e processar eficientemente a informação relevante contida em um conjunto de dados ou sinais disponíveis.

Processamento de sinais e imagens é um campo multidisciplinar da Engenharia Elétrica que tem grande interseção com ciências básicas, como a Física e a Matemática, e ciências da saúde, como a Medicina. É também essencial para integrar as contribuições das engenharias e da computação no projeto de tecnologias que interagem com os seres humanos, dispositivos, máquinas e o meio ambiente, tanto como uma ferramenta fundamental, devido aos dados envolvidos, mas também como impulsionadora de novas metodologias de pesquisa aplicada. Um dos exemplos é a utilização de processamento de imagens médicas, bem como o desenvolvimento de técnicas capazes de otimizar o tempo de processamento destas imagens, para auxiliar no diagnóstico de doenças.

Nesta área são explorados aspectos de ciência de dados aplicados a reconhecimento de padrões, visão computacional, computação gráfica, realidade virtual e aumentada, processamento de imagens, além de processamento e análise de sinais biomédicos para tecnologia assistiva.

Linhas de Pesquisa

Esta linha de pesquisa tem por objetivo mesclar conhecimentos científicos em Visão Computacional e Computação Gráfica para investigar e solucionar problemas que envolvem tecnologias imersivas com Realidade Virtual e Aumentada. No caso específico de Realidade Virtual, são investigadas questões e desafios nas áreas de ensino, medicina, entretenimento e comércio eletrônico à distância. No caso da área de Realidade Aumentada, são abordados problemas que envolvem a projeção de hologramas para aplicações na indústria, medicina, transporte, educação e interação humano-robô.

O objetivo desta linha de pesquisa é investigar as questões de software e hardware (circuitos eletrônicos dedicados) associadas à aquisição, ao processamento e à interpretação de sinais contínuos e discretos, imagens e vídeos, com intuito de abordar problemas encontrados em Processamento de Imagens, Visão Computacional, Computação em Imagens Médicas, Percepção Visual e Cognitiva, e Tecnologia Assistiva (reabilitação motora). Em particular, esta linha visa propor e implementar métodos de rastreamento de objetos em cena, descrição de cenas, segmentação e normalização espacial de imagens (2D/3D e videos), percepção visual de objetos (e.g. faces), aquisição e análise de movimentos oculares (eyetracking), mapeamento de atividades cerebrais, redes complexas, e análise de sinais biomédicos (EEG e EMG).

Esta linha de pesquisa fundamenta-se na ideia de que objetos de interesse ou padrões possam ser estudados como um conjunto de características multivariadas. Portanto, similaridades entre esses padrões podem ser investigadas e entendidas como um problema de mineração e classificação de dados. Em particular, esta linha visa propor, implementar e aplicar métodos de aprendizado de máquina (e.g. redes neurais), aprendizado estatístico, estatística multivariada e álgebra multilinear para redução de dimensionalidade e reconhecimento de padrões em imagens (2D/3D e vídeos), biometria (e.g. faces), sinais biomédicos (ECG, EEG e EMG), sinais cognitivos (eye-tracking, EEG, MEG e fMRI) e jogos (e.g. xadrez).

Disciplinas

Mestrado e doutorado

| Inteligência Artificial Aplicada à Automação e Robótica | |

|---|---|

| PEL200 - Acompanhamento de Dissertação / Tese | |

| PEL201 - Algoritmos Computacionais | |

| PEL202 - Fundamentos da Inteligência Artificial | |

| PEL208 - Tópicos Especiais em Aprendizagem | |

| PEL214 - Interação Humano-Computador em Sistemas Adaptativos | |

| PEL215 - Robótica Móvel | |

| PEL216 - Programação Científica | |

| PEL217 - Engenharia de Software em Experimentos Científicos | |

| PEL218 - Processamento de Linguagem Natural | |

| PEL219 - Redes Neurais Artificiais e Aprendizado Profundo | |

Roteiro do Processo Seletivo

PROCESSO DE INSCRIÇÃO DO MESTRADO

1º PERÍODO/2026

| Formulário de Inscrição |

| 02 cartas de recomendação (modelo padrão, baixar modelo), enviadas ao programa pela pessoa que recomenda o candidato; |

| Diploma do curso de Graduação devidamente registrado ou Atestado de Conclusão de Curso com a data da colação de grau, devidamente reconhecidos pelo Ministério da Educação ou revalidados no Brasil. |

| Histórico Escolar do curso de Graduação, devidamente reconhecido pelo Ministério da Educação. |

| Cédula de Identidade (RG) ou Carteira de Identidade Nacional (CIN), que não poderá ser substituída pela CNH; |

| Cadastro de Pessoa Física (CPF) ou comprovante de inscrição (disponível no site da Receita Federal); |

| Certidão de Nascimento ou Casamento; |

| Comprovante de residência; |

| Currículo atualizado, preferencialmente da plataforma Lattes (https://lattes.cnpq.br/); |

| 1 foto recente. |

| Ficha de Inscrição |

| 02 cartas de recomendação (modelo padrão, baixar modelo), enviadas ao programa pela pessoa que recomenda o candidato; |

| Diplomas do curso de Graduação, com a tradução juramentada (caso o mesmo não esteja em inglês ou espanhol) e autenticação do diploma estrangeiro por meio de apostilamento, caso o documento seja expedido no território de um país signatário da Convenção de Haia, ou a autenticação pela autoridade consular, no caso de país não signatário da Convenção de Haia. |

| Histórico Escolar do curso de Graduação, com tradução pública juramentada, se o documento não estiver em inglês ou espanhol. |

| RNE (Registro Nacional de Estrangeiros) ou RNM (Registro Nacional Migratório); |

| Cadastro de Pessoa Física (CPF) ou comprovante de inscrição (disponível no site da Receita Federal); |

| Número do passaporte; |

| Certificado de Proficiência em Língua Portuguesa para Estrangeiros (Celpe-Bras) com nível intermediário superior; |

| Certidão de Nascimento ou Casamento; |

| Currículo atualizado, preferencialmente da plataforma Lattes (https://lattes.cnpq.br/); |

| 1 foto recente. |

PROCESSO DE INSCRIÇÃO NO DOUTORADO

As inscrições são realizadas em fluxo contínuo, sem datas pré-fixadas. Cada candidato deve enviar por e-mail ipgss@fei.edu.br os seguintes documentos para avaliação:

| Ficha de Inscrição Solicitação de Orientador |

| Diploma da Graduação e do Curso de Mestrado (devidamente registrado pela Instituição de Ensino Superior competente) ou Atestado de Conclusão. |

| Histórico Escolar dos cursos de Graduação e Mestrado |

| Cédula de Identidade (RG) ou Carteira de Identidade Nacional (CIN), que não poderá ser substituída pela CNH; |

| CPF (Cadastro de Pessoa Física) ou comprovante de inscrição (disponível no site da Receita Federal); |

| Certidão de Nascimento ou Casamento; |

| Currículo Lattes atualizado (https://lattes.cnpq.br/); |

| 1 foto recente; |

| Projeto de Pesquisa contextualizado em uma das áreas de pesquisa do programa e, preferencialmente, já discutido com um dos professores do corpo docente. Recomenda-se a redação de um projeto de pesquisa sucinto, mas que compreenda os seguintes itens: • Resumo; • Introdução e justificativa baseados em bibliografia atualizada; • Objetivos geral e específicos; • Metodologia; • Experimentos e resultados esperados; • Plano de trabalho e cronograma de execução. |

| Ficha de Inscrição |

| Diplomas do curso de Graduação e Mestrado, com a tradução juramentada (caso o mesmo não esteja em inglês ou espanhol) e autenticação do diploma estrangeiro por meio de apostilamento, caso o documento seja expedido no território de um país signatário da Convenção de Haia, ou a autenticação pela autoridade consular, no caso de país não signatário da Convenção de Haia; |

| Históricos Escolares dos cursos de Graduação e Mestrado, com tradução juramentada (caso o mesmo não esteja em inglês ou espanhol). |

| Currículo atualizado, preferencialmente da plataforma Lattes (https://lattes.cnpq.br/); |

| Registro Nacional de Estrangeiros (RNE) ou Registro Nacional Migratório (RNM); |

| Cadastro de Pessoa Física (CPF) ou comprovante de inscrição (disponível no site da Receita Federal); |

| Certidão de Nascimento ou Casamento; |

| Certificado de Proficiência em Língua Portuguesa para Estrangeiros (Celpe-Bras) com nível intermediário superior; |

| 2 Cartas de recomendação; |

| Número do passaporte; |

| 1 foto recente; |

| Projeto de Pesquisa contextualizado em uma das áreas de pesquisa do programa e, preferencialmente, já discutido com um dos professores do corpo docente. Recomenda-se a redação de um projeto de pesquisa sucinto, mas que compreenda os seguintes itens: • Resumo; • Introdução e justificativa baseados em bibliografia atualizada; • Objetivos geral e específicos; • Metodologia; • Experimentos e resultados esperados; • Plano de trabalho e cronograma de execução. |

| Diploma do curso de Graduação, devidamente reconhecidos pelo Ministério da Educação ou revalidados no Brasil; |

| Histórico Escolar do curso de Graduação e Mestrado (se for o caso) devidamente reconhecidos pelo Ministério da Educação ou revalidados no Brasil; |

| Cédula de Identidade (RG) ou Carteira de Identidade Nacional (CIN), que não poderá ser substituída pela CNH; |

| Cadastro de Pessoa Física (CPF) ou comprovante de inscrição (disponível no site da Receita Federal); |

| Certidão de Nascimento ou Casamento; |

| Currículo Lattes atualizado (https://lattes.cnpq.br/); |

| 1 foto recente; |

| Carta de encaminhamento do orientador contendo as justificativas para a solicitação, fundamentadas no mérito e na originalidade da proposta do trabalho de pesquisa, no desempenho escolar e na maturidade científica do candidato; |

| Projeto de Pesquisa contextualizado em uma das áreas de pesquisa do programa, já discutido com um dos professores do corpo docente. Recomenda-se a redação de um projeto de pesquisa que compreenda os seguintes itens: • Resumo; • Introdução e justificativa baseados em bibliografia atualizada; • Objetivos geral e específicos; • Metodologia; • Experimentos e resultados esperados; • Plano de trabalho e cronograma de execução. |

Investimento e Bolsas

Investimentos

Bolsas de Estudo

O programa de Mestrado e Doutorado em Engenharia Elétrica da FEI conta com bolsas da agência de fomento federal CAPES para dedicação em tempo integral e parcial. A FEI oferece, também, bolsas de isenção de pagamento de taxas escolares. Os alunos interessados em obter bolsa de estudos devem protocolar solicitação no ato da matrícula. Os critérios para concessão da bolsa são baseados na avaliação de mérito do desempenho acadêmico e da experiência profissional dos alunos aprovados no processo seletivo. Além disso, os alunos que solicitam bolsa para dedicação em tempo integral devem ter disponibilidade de 40 horas semanais e não possuir vínculo empregatício. Já a solicitação de bolsa para dedicação em tempo parcial requer disponibilidade de 20 horas semanais, podendo o aluno acumular o benefício com exercício profissional remunerado.

Os alunos de Mestrado e Doutorado podem também solicitar bolsas de estudo externas em órgãos de fomento como:

FAPESP: A Fundação de Amparo à Pesquisa do Estado de São Paulo é uma das principais agências de fomento à pesquisa científica e tecnológica do país. A FAPESP está ligada à Secretaria de Desenvolvimento Econômico, Ciência, Tecnologia e Inovação do Estado de São Paulo.

Veja como solicitar no site da Fapesp.

CNPq: O Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) é uma agência do Ministério da Ciência e Tecnologia (MCT) destinada ao fomento da pesquisa científica e tecnológica e à formação de recursos humanos para a pesquisa no país. O CNPq oferece várias modalidades de bolsas aos alunos de mestrado e doutorado.

Veja como solicitar no site do CNPq.

Pós-doutorado

A Pós-graduação Stricto Sensu em Administração do Centro Universitário FEI desce 2014 conta com um programa de Pós-Doutorado.

O candidato selecionado é contemplado com bolsa PNPD-CAPES e também recebe uma bolsa suplementar da FEI pelo período de um ano, podendo ser estendido por mais um. O pós-doutorando, assim como os professores do programa tem a sua disposição uma sala/escritório para trabalhar e tem acesso aos recursos necessários para desenvolver suas atividades de pesquisa.

O pesquisador deve participar em projetos de pesquisa em parceria com um dos professores do Programa e poderá desenvolver colaborações com os outros professores e alunos do Mestrado e Doutorado.

Ao final do programa o pesquisador receberá um certificado após ter submetido um artigo científico a um periódico internacional de alto impacto e apresentar um seminário de pesquisa no tema desenvolvido.

Processo Seletivo

Procuramos pesquisadores que desejam aprimorar suas habilidades de pesquisa e ensino de excelência e alto impacto científico.

Estágio Pós-doutoral em andamento

• Mariana Lima Bandeira

Estágios Pós-doutorais concluídos

• Renata Fernandes Galhanone

• Cristiane Gattaz

Formulários, Regimento e Normas

Mestrado/Doutorado

DEPÓSITO DISSERTAÇÃO/TESE

- PGSS 13.0 Depósito de Dissertação e Tese

- Depósito - Declaração versão final 60 dias

- Depósito - Não violação direitos autorais

FORMULÁRIOS DIVERSOS

Normas

Corpo Docente

Mestrado e Doutorado em Engenharia Elétrica

Docentes Colaboradores

Os docentes colaboradores integram o corpo docente do Programa e participam de forma sistemática do desenvolvimento de projetos de pesquisa ou atividades de ensino ou extensão e/ou orientação de estudantes.